TSMC لیتوگرافی 1.6 نانومتری خود را با عملکرد و کارایی قابل توجهی معرفی کرد

TSMC فرآیند تولید 1.6 نانومتری پیشگامانه خود را برای تراشه ها ارائه کرد و همچنین شامل شبکه پاور دلیوری در پشت است که بازده برق و تراکم ترانزیستور را حتی بیشتر بهبود می بخشد. فرآیند 1.6 نانومتری معرفی شده، درست مانند معماریهای آینده N2، N2P و N2X مبتنی بر نود های 2 نانومتری، به ترانزیستورهای نانوصفحه گیتدار متکی است.

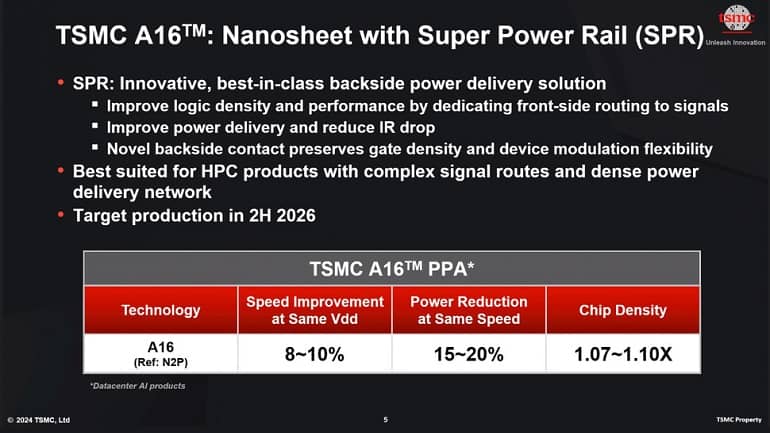

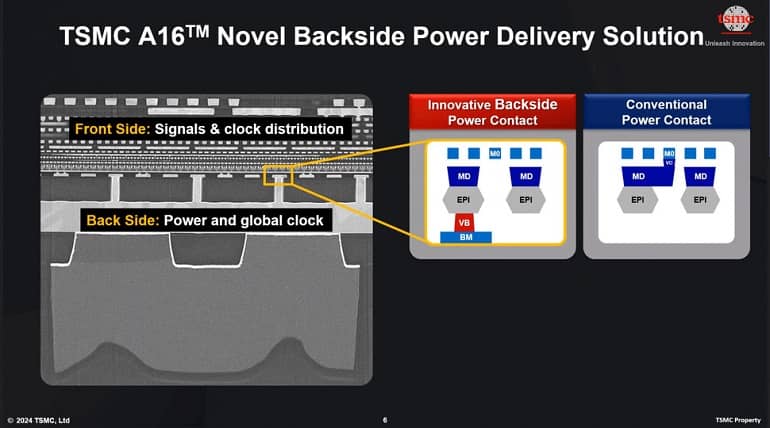

فرآیند جدید به تنهایی 10 درصد سرعت کلاک بالاتر در ولتاژ یکسان و تا 20 درصد تخلیه انرژی کمتر در فرکانس و پیچیدگی یکسان را امکان پذیر می کند. بسته به طراحی تراشه، فرآیند 1.6 نانومتری جدید می تواند تا 10 درصد ترانزیستورهای بیشتری را نیز در خود جای دهد. شبکه پاور دلیوری پشتی احتمالاً جنبه چشمگیرتری از این تراشههای آینده است زیرا تراکم ترانزیستور را افزایش میدهد و انتقال توان را بهبود میبخشد که به نوبه خود بر عملکرد تأثیر میگذارد.

TSMC میگوید که همراه با Super Power Rail (SPR)، که نوع دوشاخهای است که برای اتصال تراشه به منبع برق استفاده میشود، شبکه پاور دلیوری پشتی عمدتاً برای پردازندههای AI و HPC که به سیمکشی سیگنال پیچیده و شبکههای قدرت متراکم نیاز دارند، مفید خواهد بود. جدول زمانی تولید برای نیمه دوم سال 2026 برنامه ریزی شده است، اگر همه چیز طبق برنامه پیش برود، اولین محصولات آماده مصرف کننده در سال 2027 ارسال می شود.